据外媒 Neowin 报道,优化芯片设计是提高当今系统计算能力的关键。然而这是一个需要花费大量时间的过程,人们正在努力使其更有效率。考虑到这一点,现在谷歌研究人员已经将目光投向了机器学习,以帮助解决这个问题。

在最近发表在《arXiv 上》的一篇题为 "通过深度强化学习进行芯片布局(Chip Placement with Deep Reinforcement Learning) "的论文中,谷歌的团队将芯片布局问题定位为强化学习(RL)问题。然后,训练好的模型将芯片 block(每个芯片 block 都是一个独立的模块,如内存子系统、计算单元或控制逻辑系统)放置到芯片画布上。

确定芯片 block 的布局,这个过程被称为芯片布局规划,是芯片设计过程中最复杂和最耗时的阶段之一,它涉及到将网表放置到芯片画布(2D 网格)上,这样可以使功率、性能和面积(PPA)最小化,同时遵守密度和布线拥塞方面的限制。尽管在这个问题上已经进行了数十年的研究,但仍然需要人类专家进行数周的迭代,以产生满足多方面设计标准的解决方案。

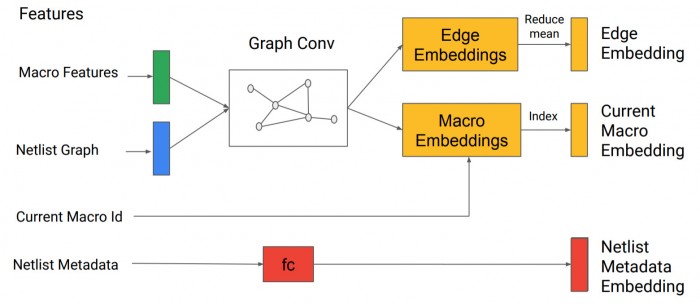

深度强化学习模型的输入是芯片网表、当前要放置节点的 ID 和一些网表元数据。网表图和当前节点通过一个基于边缘的图神经网络来生成部分放置的图和候选节点的嵌入。

然后,前馈神经网络将其作为一个聚合输入,输出一个学习到的表示方法,该方法可以捕捉有用的特征,并帮助在所有可能的网格单元中生成一个概率分布,通过策略网络可以将当前节点放置在该节点上。整个过程可以用下面的 GIF 来封装。左边的芯片显示了从头进行的宏放置,右边的芯片则是对一些初始放置进行微调。

通过这种设置,研究人员展示了效率和放置质量的提高,并表示对于一个人类专家需要数周时间的过程,用他们训练有素的 ML 模型在 6 个小时内完成。

我们的目标是将 PPA(功率、性能和面积)降到最低,我们表明,在 6 个小时内,我们的方法可以产生出在现代加速器网表上的超人类或可比性的安置,而现有的基线需要人类专家在循环中进行,需要几周的时间。

展望未来,该团队认为,其模型展示了一种强大的自动芯片布局方法,可以大大加快芯片设计的速度,这也是针对任何芯片布局问题,这将使芯片设计过程的早期阶段也能实现协同优化。

- 版权声明:文章来源于网络采集,版权归原创者所有,均已注明来源,如未注明可能来源未知,如有侵权请联系管理员删除。